计算机原理接口硬件软件RISC-V版 设计RISC主板必学的CPU知识 211M极品 顶级珍贵资料 ,网上难找。

”risc-v 计算机原理接口硬件软件RISCv“ 的搜索结果

学习开发一个RISC-V的操作系统的学习笔记,在Ubuntu 20.04上开发一个简易的操作系统。本系列持续不定期更新,分享出来和大家一同交流进步。

计算机的语言2.1 引言2.2 计算机硬件的操作2.3 计算机硬件的操作数2.3.1 ...计算机硬件对过程的支持2.8.1 使用更多的寄存器2.8.2 嵌套过程2.8.3 在栈中为新数据分配空间2.8.4 在堆中为新数据分配空间2.9 人机交互2.10 ...

摆烂才是王道

计算机组成原理:硬件/软件接口 第五版英文原版答案 《计算机组成与设计:硬件/软件接口(原书第5版)》是计算机组成与设计的经典畅销教材,第5版经过全面更新,关注后PC时代发生在计算机体系结构领域的革命性变革...

指令集架构(instruction set architecture):是底层硬件电路面向上层应用程序提供的一层接口规范。基本数据类型(byte,halfword,word)寄存器指令寻址模式异常或者中断的处理方式等等。。也就是操作系统和底层...

计算机组成与设计-硬件软件接口 RISC-V版Chapter2指令集RISC-V简介RISC-V基本语法 Chapter2 指令集 The words of a computer’s language are called instructions, and its vocabulary is called an instruction ...

Computer Organization and Design - The Hardware Software Interface [RISC-V Edition] Solution Manual

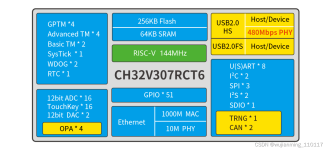

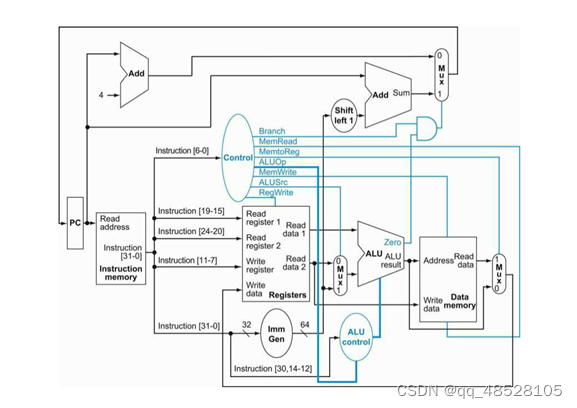

本文采用RISC-V架构设计CPU,实现单周期CPU,设计取指、译码、执行、访存、写回五个阶段,扩展实现了RV32I指令集,通过该指令集所有指令的仿真测试。工具采用了iverilog和GTKwave。(具体仿真调试过程见下一篇文章)

立即数imm由立即数生成模块生成,根据I型运算类指令的指令格式,I型立即数的低12位imm[11:0]来自指令的31~20位,按照符号位扩展方法扩展得到32位立即数送给ALU, ALU完成具体的运算,运算的结果通过寄存器堆的数据写...

在今年6 月 27 日,中国移动正式发布全球首颗纯自研 RISC-V 架构的 LTE-Cat.1 芯片和移动首颗纯自研量产的蜂窝物联网通信芯片,他们分别是CM8610 LTE-Cat.1和CM6620 NB-IoT,两者在功耗,计算性能,射频性能上都非常...

基于多核异构架构,集成RISC-V 指令架构的四核C910 和单核C906 处理器,并内嵌了多个强大硬件加速引擎,搭载4TOPS@int8 AI 算力的NPU,提供性能优化的高端应用。支持双通道外部存储器接口,支持LPDDR4/LPDDR4X,提供...

物联网(IoT)是一项持续的技术革命。嵌入式处理器是智能物联网设备的处理引擎...为了处理可预见的安全威胁,RISC-V社区正在研究旨在实现信任根 (RoT) 的安全解决方案,并确保 RISC-V 设备上的敏感信息不会被篡改或泄露。

介绍几种比较著名的 CPU 架构

推荐文章

- YOLOv7如何提高目标检测的速度和精度,基于优化算法提高目标检测速度-程序员宅基地

- linux中进程退出函数:exit()和_exit()的区别_linux结束进程可以用哪些函数,它们之间有何区别?-程序员宅基地

- sqlserver55555_sqlserver把小数点后面多余的0去掉-程序员宅基地

- Angular6 和 RXJS6 的一些改动_angular6,requestoptions改成了什么-程序员宅基地

- C++解析XML文件_c++ xml解析-程序员宅基地

- R语言使用caret包的train函数构建多元自适应回归样条(MARS)模型构建分类模型、trainControl函数设置交叉验证参数、自定义调优评估指标_多元自适应回归样条 r-程序员宅基地

- Android ListView控件显示数据库中图片_安卓获取listview里的图片并显示-程序员宅基地

- python123程序改错题库,2016最新二级C语言考试题库及答案(程序改错专项练习 精华版)...-程序员宅基地

- Roser S.Pressman在UMLChina交流实录-程序员宅基地

- 【Linux】shell编程1(shell脚本书写格式、脚本中的环境变量、普通变量、自定义环境变量、变量数组、位置变量、状态变量、内置变量、变量扩展)_linux脚本格式-程序员宅基地